Potřebuji detekovat vzestupnou hranu vstupního signálu a vygenerovat krátký impulz, který přepne S-R trigger.

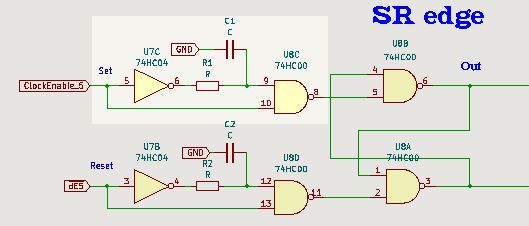

Používám obvody 74HC00 a 74HC04, zapojení na připojeném obrázku. S náhodným odporem (asi 0.2-10 kOhm?) a kondenzátorem 66nF to funguje, bez RC členu (odpor, kondenzátor) to nefunguje, protože samotné zpoždění na hradle NOT nestačí pro překlopení S-R (pravá dvě NAND).

Ta vysvícená část funguje tak, že když se vstup změní z nuly na jedničku, tak za tím NOT je na vstupu í ještě chvíli jednička, dokud se ten kondenzátor nevybije přez ten odpor natolik, že to napětí klesne dost. Ten NAND má teda chvíli jedničku na obou vstupech a tudíž nulu na výstupu a tou přepne ten S-R obvod vpravo.

Mohl bych zkusit někde sehnat přístup v osciloskopu a zkoušet různé součástky, ale myslím si, že by to mělo jít nějak zhruba spočítat. Poradí někdo?

0x

Nie som si isty, ci chapem poziadavku spravne : vas ciel je trvalo preklopit vystup, ked je na vstupe clock enable vzostupna hrana? Ak ano, potom je uplne zbytocne strkat tam RC cleny, postaci klopny obvod reagujuci na vzostupnu hranu a priviest mu na datovy vstup trvalu jednotku. Obvod 74 HC 74 obsahuje dva take obvody, ma to aj reset.

Ono je to součást většího celku (tady o tom mám nějaké poznámky 8bit.gilhad.cz/... ) potřebuju udělat obvod (7x) který bude mít:

Jeden výstup a dva vstupy, náběžná hrana na jednom vstupu přepíná výstup do HIGH, náběžná hrana na druhém ho přepíná do LOW

Výstup zůstává v poslední nastavené hodnotě, dokud nepřijde další náběžná hrana někam.

Opakované náběžné hrany na témže vstupu opakovaně nastavují výstup na tuttéž hodnotu.

Celkově by to mělo tak nějak zabírat co nejmíň pouzder pro celkem 7 těchto obvodů (potřebuju 7 semaforů (tedy celý ten šedá obrázek) pro sdílené prostředky), při rozumné ceně (ušetřit jedno pouzdro za cenu extra drahé součástky nechci, u stejného počtu pouzder vítězí běžnější chipy a jednodušší design - už jsem vyměnil ta dvě NAND vpravo, co dělají S-R obvod za 1/4 74HC279).

Na těch vstupech se napětí mění "náhodně", přistupují k tomu dva různé systémy, které běží na nesoudělných frekvencích a každý dělá něco jiného a jinak a tohle je přesně ten modul, přez který komunikují. Události se tam dějí někde okolo té 1MHz rychlosti, principiálně by neměly přijít dvě vzestupné hrany prakticky naráz, pokud by se tak stalo, je jedno v jakém stavu výstup skončí.

Neneseme odpovědnost za správnost informací a za škodu vzniklou jejich využitím. Jednotlivé odpovědi vyjadřují názory jejich autorů a nemusí se shodovat s názorem provozovatele poradny Poradte.cz.

Používáním poradny vyjadřujete souhlas s personifikovanou reklamou, která pomáhá financovat tento server, děkujeme.